Η Quotidiano economico di Taiwan lui sostiene che il TSMC raggiunto una significativa scoperta interna per il suo smaltimento finale tecnologia litografia 2 nm.

ΣSecondo la pubblicazione, questa pietra miliare consente a TSMC di è ottimista su un'implementazione della prima produzione "Risk Production" 2 nm nel 2023.

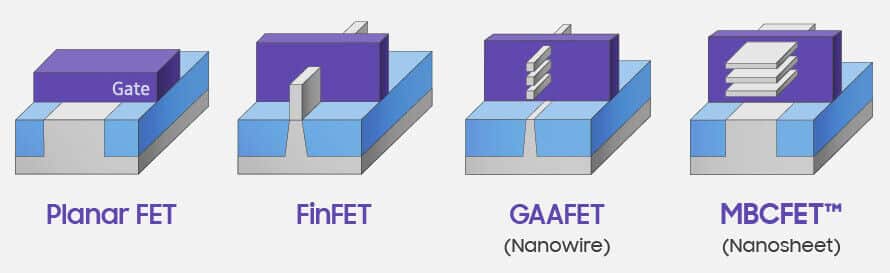

Ancora impressionanti sono i rapporti che TSMC abbandona la tecnologia FinFet per un nuovo transistor ad effetto di campo (MBCFET) a canale multi-ponte basato sulla tecnologia Gate-All-Around (GAA). Questa importante scoperta sta arrivando un anno dopo la creazione di un team indoor da parte di TSMC, il cui obiettivo era aprire la strada allo sviluppo della litografia a 2 nm.

La tecnologia MBCFET estende l'architettura GAAFET prendendo il transistor ad effetto di campo Nanowire e "diffondendolo" per diventare un Nanosheet. L'idea principale è quella di realizzare il transistor ad effetto di campo XNUMXD.

Questo nuovo transistor semiconduttore a ossido di metallo complementare può migliorare il controllo del circuito e ridurre la dispersione di corrente. Questa filosofia di design non è esclusiva di TSMC - Samsung prevede di sviluppare una variazione di questo design nella loro tecnologia di litografia 3 nm.

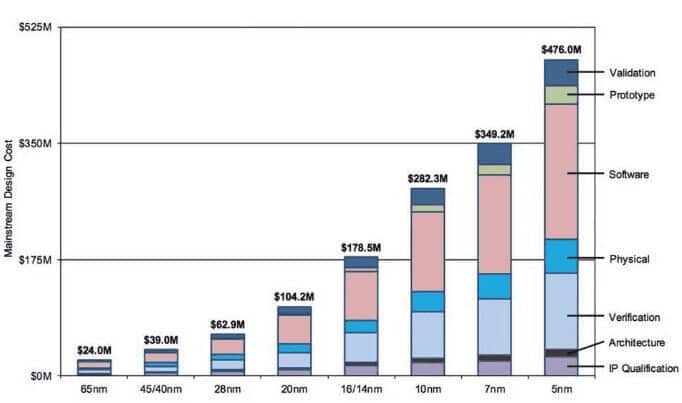

Come di solito, un'ulteriore riduzione della scala di produzione dei chip ha un costo enorme. In particolare, il costo di sviluppo per la litografia a 5 nm ha già raggiunto i 476 milioni di dollari, mentre Samsung afferma che la tecnologia GAA di 3 nm costerà oltre 500 milioni di dollari. Naturalmente, lo sviluppo della litografia 2 nm, supererà questi importi...

Non dimenticare di seguirlo Xiaomi-miui.gr a Google News per essere subito informato su tutti i nostri nuovi articoli!

Non dimenticare di seguirlo Xiaomi-miui.gr a Google News per essere subito informato su tutti i nostri nuovi articoli!